Mục đích

- Làm quen và nắm vững các nguyên tắc và phương pháp thiết kế tệp đăng ký trong máy tính MIPS

- Hiểu khái niệm toán hạng nguồn/toán hạng đích

Môi trường thử nghiệm

- Môi trường phát triển tích hợp Vivado

Thanh ghi MIPS

- đăng ký R0 Giá trị của luôn luôn là 0 .

Thiết kế giao diện mô-đun

1 cổng ghi và 2 cổng đọc.

| tên |

chiều rộng |

phương hướng |

mô tả |

| tiếng kêu |

1 |

TRONG |

Tín hiệu đồng hồ |

| raddr1 |

5 |

TRONG |

Đăng ký tập tin đọc địa chỉ 1 |

| rdata1 |

32 |

NGOÀI |

Đăng ký dữ liệu trả về tập tin 1 |

| raddr2 |

5 |

TRONG |

Đăng ký tập tin đọc địa chỉ 2 |

| rdata2 |

32 |

NGOÀI |

Đăng ký dữ liệu trả về tập tin 2 |

| chúng tôi |

1 |

TRONG |

Đăng ký cho phép ghi tệp |

| waddr |

5 |

TRONG |

Đăng ký địa chỉ ghi ngăn xếp |

| dữ liệu w |

32 |

TRONG |

Đăng ký ngăn xếp ghi dữ liệu |

Tệp đăng ký (regfile) triển khai ba mươi hai thanh ghi mục đích chung 32 bit.

- Có thể đọc hai thanh ghi và ghi một thanh ghi cùng một lúc.

- Ghi: Khi tín hiệu cho phép ghi (we) là 1, việc ghi là hợp lệ, và khi bằng 0, việc ghi là không hợp lệ. ( viết cho phép )

- Đọc: Một thao tác đọc có thể đọc hai thanh ghi cùng một lúc.

- Khi đọc và ghi cùng một thanh ghi cùng một lúc, dữ liệu được đọc là dữ liệu cũ.

- Cả đọc và viết đều diễn ra đồng bộ.

- Thanh ghi 0 luôn luôn là 0.

Mã thiết kế

`define REG_DATA_WIDTH 31:0 `define REG_NUM 31:0 `define REG_ADDR_WIDTH 4:0 `define REG_ADDR_BIT 5 // Độ rộng đường địa chỉ`define REG_DATA_BIT 32 // Độ rộng đường dữ liệumodule regfile( input clk, input [`REG_ADDR_WIDTH] raddr1, input [`REG_ADDR_WIDTH] raddr2, input we, // Write enableinput [`REG_ADDR_WIDTH] waddr, // Write addressinput [`REG_DATA_WIDTH] wdata, // Write dataoutput reg [`REG_DATA_WIDTH] rdata1, output reg [`REG_DATA_WIDTH] rdata2 ); // Mảng biểu diễn thanh ghi stackreg [`REG_DATA_WIDTH] mips_regfile [`REG_NUM]; // luôn đọc 1 @(posedge clk) bắt đầu nếu (raddr1 == {`REG_ADDR_BIT{1'b0}}) bắt đầu rdata1 <= {`REG_DATA_BIT{1'b0}}; kết thúc nếu không thì bắt đầu rdata1 <= mips_regfile[raddr1]; kết thúc kết thúc // luôn đọc 2 @(posedge clk) bắt đầu nếu (raddr2 == {`REG_ADDR_BIT{1'b0}}) bắt đầu rdata2 <= {`REG_DATA_BIT{1'b0}}; kết thúc nếu không thì bắt đầu rdata2 <= mips_regfile[raddr2]; kết thúc kết thúc // luôn ghi @(posedge clk) bắt đầu nếu (we == 1'b1 ) bắt đầu nếu (waddr == {`REG_ADDR_BIT{1'b0}}) bắt đầu mips_regfile[0] <= {`REG_DATA_BIT{1'b0}}; kết thúc nếu không thì bắt đầu mips_regfile[waddr] <= wdata; kết thúc kết thúc nếu không bắt đầu mips_regfile[0] <= {`REG_DATA_BIT{1'b0}}; kết thúc kết thúc endmodule

Bài kiểm tra

Mã kiểm tra

`timescale 1ns / 1ps `define REG_DATA_WIDTH 31:0 `define REG_NUM 31:0 `define REG_ADDR_WIDTH 4:0 `define REG_ADDR_BIT 5 `define REG_DATA_BIT 32 module sim(); reg clk; reg [`REG_ADDR_WIDTH] raddr1; reg [`REG_ADDR_WIDTH] raddr2; reg we; // cho phép ghi reg [`REG_ADDR_WIDTH] waddr; // ghi địa chỉ reg [`REG_DATA_WIDTH] wdata; // ghi dữ liệu dây [`REG_DATA_WIDTH] rdata1; dây [`REG_DATA_WIDTH] rdata2; số nguyên i; tệp reg u0 ( .clk(clk), .raddr1(raddr1), .raddr2(raddr2), .we(we), .waddr(waddr), .wdata(wdata), .rdata1(rdata1), .rdata2(rdata2) ); khởi tạo clk = 1; khởi tạo mãi mãi #10 clk = ~clk; kết thúc kết thúc khởi tạo raddr1 = `REG_ADDR_BIT'd0; raddr2 = `REG_ADDR_BIT'd0; we = 1'b0; waddr = `REG_ADDR_BIT'd0; wdata = `REG_DATA_BIT'd0; // Lệnh #100 we = 1'b1; wdata = `REG_DATA_BIT'hFF; for (i = 0; i < `REG_DATA_BIT; i = i + 1) bắt đầu waddr = i; wdata = wdata + `REG_DATA_BIT'h100; #20; end // đọc dữ liệu we = 1'b0; for (i = 0; i < `REG_DATA_BIT; i = i + 1) begin raddr1 = i; raddr2 = `REG_DATA_BIT - raddr1 - 1; #20; end // đọc và ghi giống nhau // dữ liệu đọc là dữ liệu cũ we = 1'b1; wdata = `REG_DATA_BIT'h100; for (i = 0; i < `REG_DATA_BIT; i = i + 1) begin raddr1 = i; raddr2 = i; waddr = i; wdata = wdata - `REG_DATA_BIT'h1; #20; end we = 1'b0; #100 $finish; end endmodule

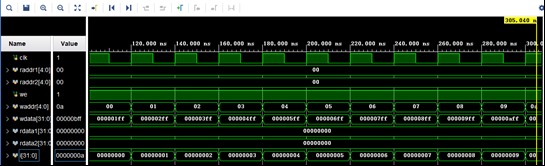

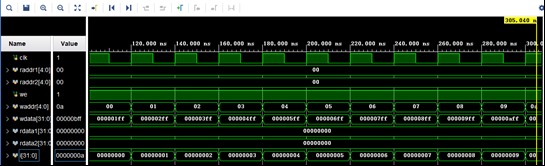

Kiểm tra dạng sóng

Ghi dữ liệu:

Bắt đầu từ thanh ghi 0 đến thanh ghi 31, ghi lần lượt từ 01ff đến 20ff.

Đọc dữ liệu:

Đọc địa chỉ 1 và đọc địa chỉ 2 lần lượt đọc giá trị thanh ghi, giá trị đọc được từ thanh ghi 0 là 0. Các thanh ghi còn lại đều đọc chính xác.

Phân tích kết quả

Đầu tiên, thực hiện thử nghiệm ghi dữ liệu, bắt đầu từ thanh ghi 0 đến thanh ghi 31, ghi lần lượt từ 01ff đến 20ff. Sau đó, tiến hành thử nghiệm đọc dữ liệu và thấy rằng giá trị của thanh ghi 0 là 0, các giá trị của các thanh ghi còn lại đều như mong đợi. Khi ghi và đọc cùng lúc, tức là địa chỉ ghi và địa chỉ đọc giống nhau, đồng thời bật chức năng ghi thì phát hiện dữ liệu đọc là dữ liệu cũ, dữ liệu ghi sẽ không xung đột.

Cuối cùng, bài viết này về tệp đăng ký MIPS kết thúc tại đây. Nếu bạn muốn biết thêm về tệp đăng ký MIPS, vui lòng tìm kiếm các bài viết CFSDN hoặc tiếp tục duyệt các bài viết liên quan. Tôi hy vọng bạn sẽ ủng hộ blog của tôi trong tương lai! .

Tôi là một lập trình viên xuất sắc, rất giỏi!